同步时序逻辑电路中的无效状态是由于状态表没有达到最简导致的。

第1题:

同步时序逻辑电路的设计中,触发器个数与电路中包含的状态数有关。()

第2题:

A、使用的隐含表不同

B、等效概念和相容概念的不同

C、最大等效类与最大相容类得到的方法不同

D、最小化状态表中某个状态得到的方法不同

第3题:

A、列写逻辑方程式

B、计算状态表

C、画电路的状态图

D、画电路的时序图

E、判定电路的功能

第4题:

第5题:

第6题:

A、状态等效是完全给定同步时序电路设计中的一个概念

B、状态等效不具有传递性

C、等效的状态可以合并为一个状态

D、最简化状态表中的每一个状态是一个最大等效类

第7题:

根据输出信号的特点可将时序电路分为()

A、Mealy型

B、Moore型

C、同步时序逻辑电路

D、异步时序逻辑电路

第8题:

在同步时序电路的设计中,若最简状态表中的状态数为2N,而又是用N级触发器来实现其电路,则不需检查电路的自启动性。()

第9题:

第10题:

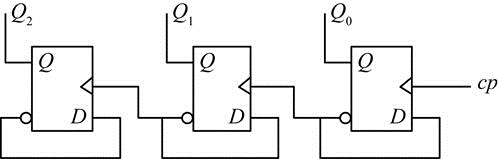

由于移位寄存器各级触发器是在同一时钟作用下发生状态转移,所以是同步时序逻辑电路。