通常,8253-5是在时钟脉冲CLK的()时刻,采样门控信号GATE。

第1题:

8253-5工作于方式3时,当计数值为一奇数时,则输出信号的低电平比高电平持续时间()

第2题:

8253-5工作于方式3时,方波的重复周期是()。

第3题:

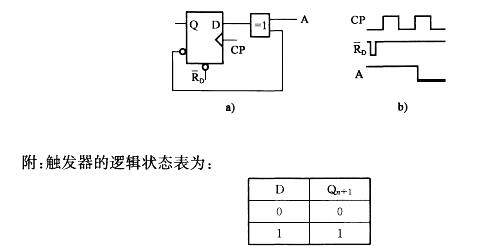

,信号A及时钟脉冲信号cp如图b)所示,经分析可知,在第一个和第二个时钟脉冲的下降沿时刻,输出Q分别等于:

,信号A及时钟脉冲信号cp如图b)所示,经分析可知,在第一个和第二个时钟脉冲的下降沿时刻,输出Q分别等于:

第4题:

8253-5工作于方式0当将计数值写入初值计数器后,是在下一个CLK脉冲的()时装入计数执行单元CE中。再从下一个CLK脉冲的()开始,CE减1计数。

第5题:

8253-5工作于方式2时,若计数值为N时,每输入N个CLK脉冲,则输出()

第6题:

8253定时器/数器中,在门控制信号上升沿到来后的()时刻,输出信号OUT变成低电平。

第7题:

8253-5工作于方式0和方式4时,门控信号为()触发。

第8题:

8253—5工作于方式1时,当门控信号上升沿到来后的()时刻,门控信号OUT变成低电平。

第9题:

8253-5工作于方式1时,当门控信号GATE()到来后的下一个时钟脉冲CLK信号的(),才将写入CR中的计数初值装入计数执行单元CE。

第10题:

试说明8253芯片的六种工作方式。其时钟信号CLK和门控信号GATE分别起什么作用?