第1题:

关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

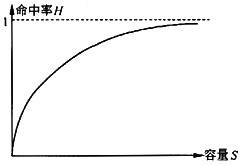

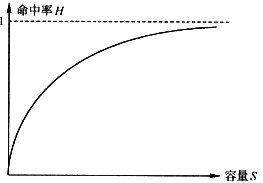

D.Cache的命中率只与其容量相关

第2题:

多处理机的存储器体系结构分为()和()存储器体系结构两种。

第3题:

以下关于Cache(高速缓冲存储器)的描述,(9)是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第4题:

在Cache实现的两种写策略中,()的速度快,“写”操作能以Cache存储器速度进行,访存次数少;采用()总能保持Cache和主存内容的一致。

第5题:

简述在分布式共享存储器体系结构中目录协议中目录的含义。

第6题:

简述维护Cache一致性的两种共享数据跟踪技术。

第7题:

简述cache的两种写调块策略。

第8题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第9题:

简述在集中式共享存储器体系结构中两种维护Cache一致性的两种协议。

第10题:

下面是主存储器和CAChe的比较,正确的有()