小于16

大于16

等于16

任意

第1题:

已知某可编程接口芯片中计数器的口地址为40H,计数频率为MHz,该芯片的控制字为 8位二进制数。控制字寄存数的口地址为43H,计数器达到0值的输出信号用作中断请求信号,执行下列程序后,发出中断请求信号的周期是【 】ms。

MOV AL,00110110B ;计数器按二进制计数,16位读/写,

;可自动装载计数器初值

OUT 43H,AL

MOV AL,0FFH

OUT 40H,AL

OUT 40H,AL

第2题:

如果芯片8253的控制字为0AAH,则8253各计数器的工作方式是

A.计数器0工作在模式1

B.计数器1工作在模式5

C.计数器1按二进制计数方式工作

D.计数器2按二进制计数方式工作

E.计数器2工作在模式5

第3题:

此题为判断题(对,错)。

第4题:

第5题:

第6题:

此题为判断题(对,错)。

第7题:

第8题:

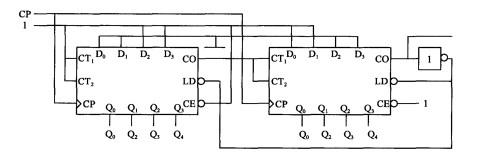

通常将二进制计数器与五进制计数器上串,可得到十进制计数器,若将十进制计数器与六进制计数器相串,可得十六进制计数器。()

第9题:

第10题: