以下关于计算机系统中高速缓存(Cache)的说法中,正确的是( )。

A. Cache 的容量通常大于主存的存储容量 B.通常由程序员设置 Cache 的内容和访问速度 C.Cache 的内容是主存内容的副本 D.多级 Cache 仅在多核 CPU 中使用

第1题:

A.Cache扩充了主存储器的容量

B.Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

C.Cache的有效性是利用了对主存储器访问的局部特征

D.Cache中通常保存着主存储器中部分内容的一份副本

Cache,即高速缓冲存储器。Cache的出现是基于两个原因。首先是由于CPU的速度和性能提高很快而主存速度较低且价格高,其次就是程序执行的局部性特点。因此,将速度比较快而容量有限的SRAM构成Cache,目的在于尽可能发挥CPU的高速度。Cache位于CPU和主存之间,其内容是主存内容的副本。

第2题:

以下关于cache的途述中,正确的是________。

A.cache和主存都用半导体芯片作为存储介质,因此它们的存取速度相差不大

B.在程序中不能用数据传送指令读出cache中某个单元中存储的内容

C.cache存储容量的大小对计算机的运行速度会产生影响

D.只有将一个程序的全部指令从内存装入cache才能在CPU中运行该程序

第3题:

● 以下关于Cache的叙述中,正确的是 (4) 。

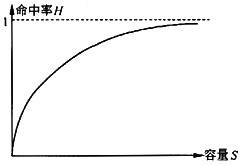

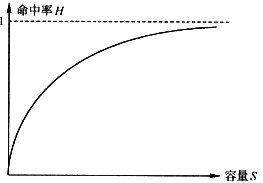

A. 在容量确定的情况下,替换算法的时间复杂度是影响Cache命中率的关键因素

B. Cache的设计思想是在合理成本下提高命中率

C. Cache的设计目标是容量尽可能与主存容量相等

D. CPU 中的Cache容量应大于CPU 之外的Cache容量

第4题:

以下关于CPU与主存之问增加高速缓存(Cache)的叙述中,错误的是______。

A.Cache扩充了主存储器的容量

B.Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

C.Cache的有效性是利用了对主存储器访问的局部性特征

D.Cache中通常保存着主存储器中部分内容的一份副本

A.

B.

C.

D.

第5题:

● 以下关于Cache的叙述中,正确的是 (10) 。

(10)

A. 在容量确定的情况下,替换算法的时间复杂度是影响Cache命中率的关键因素

B. Cache的设计思想是在合理的成本下提高命中率

C. Cache的设计目标是容量尽可能与主存容量相等

D. CPU中的Cache容量应大于CPU之外的Cache容量

第6题:

● 以下关于CPU与主存之间增加高速缓存(Cache)的叙述,不正确的是 (7) 。

(7)

A. Cache扩充了主存储器的容量

B. Cache可以降低由于CPU 与主存之间的速度差异造成的系统性能影响

C. Cache的有效性是利用了对主存储器访问的局部性特征

D. Cache中通常保存着主存储器中部分内容的一份副本

第7题:

以下关于Cache(高速缓冲存储器)的描述,(9)是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第8题:

● 以下关于CPU 与主存之间增加高速缓存(Cache)的叙述中,错误的是 (4) 。

(4)

A. Cache扩充了主存储器的容量

B. Cache可以降低由于CPU 与主存之间的速度差异造成的系统性能影响

C. Cache的有效性是利用了对主存储器访问的局部性特征

D. Cache中通常保存着主存储器中部分内容的一份副本

第9题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第10题:

关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关