关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第1题:

第2题:

第3题:

● 下面关于 Cache(高速缓冲存储器)的叙述, “ (9) ”是错误的。

(9)

A. 在体系结构上,Cache 存储器位于主存与 CPU之间

B. Cache 存储器存储的内容是主存部分内容的拷贝

C. 使用 Cache 存储器并不能扩大主存的容量

D. Cache 的命中率只与其容量相关

第4题:

● 以下关于Cache(高速缓冲存储器)的描述, (9) 是错误的。

(9)

A. 在体系结构上,Cache存储器位于主存与CPU 之间

B. Cache存储器存储的内容是主存部分内容的拷贝

C. 使用Cache存储器并不能扩大主存的容量

D. Cache的命中率只与其容量相关

第5题:

● 关于Cache(高速缓冲存储器)的说法中,错误的是(9)

(9)

A. 在体系结构上,Cache存储器位于主存与CPU 之间

B. Cache存储器存储的内容是主存部分内容的拷贝

C. 使用Cache存储器并不能扩大主存的容量

D. Cache的命中率只与其容量相关

第6题:

答案及其解析——位于CPU与主存之间的高速缓冲存储器(Cache)用于存放部分主存数据的拷贝,主存地址与Cache地址之间的转换工作由_____完成。

第7题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

第8题:

高速缓冲存储器Cache是位于CPU和主存DRAM之间的小容量高速存储器,其采用的是______类型存储器。

第9题:

以下关于Cache(高速缓冲存储器)的描述,(9)是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

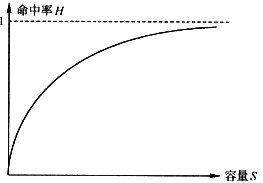

D.Cache的命中率只与其容量相关