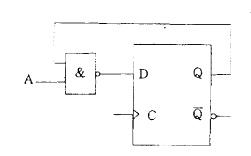

第1题:

A.1

B.0

C.保持

D.不定态

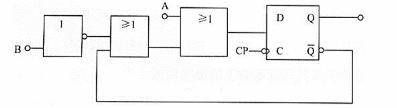

第2题:

第3题:

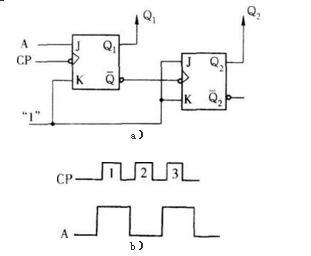

由JK触发器装换成的T触发器,其输出状态在CP脉冲的()时变化。

A.高电平

B.低电平

C.上升沿到来

D.下降沿到来

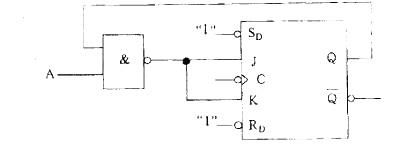

第4题:

第5题:

第6题:

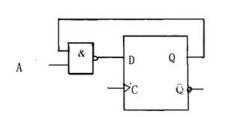

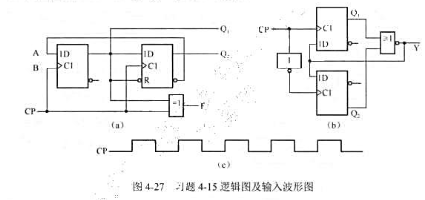

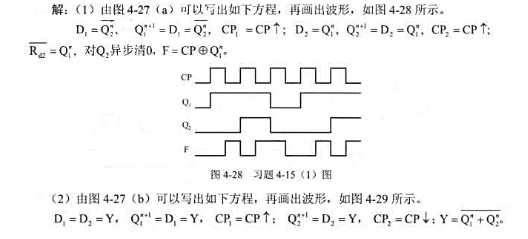

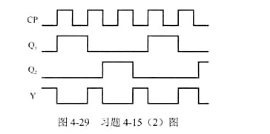

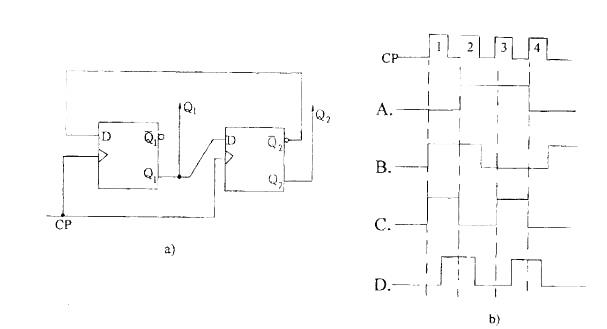

图4-27(a),(b)分别示出了触发器和逻辑门构成的脉冲分频器电路,CP脉冲如图4-27(c)所示,各触发器的初始状态皆为0.

(1)试画出图4-27(a)的Q1、Q2和F的波形.

(2)试画出图4-27(b)的Q1、Q2和Y的波形.

第7题:

第8题:

此题为判断题(对,错)。

第9题:

第10题: