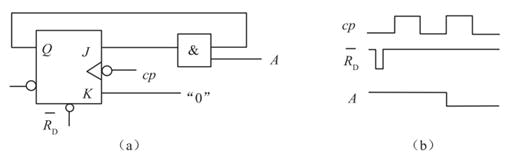

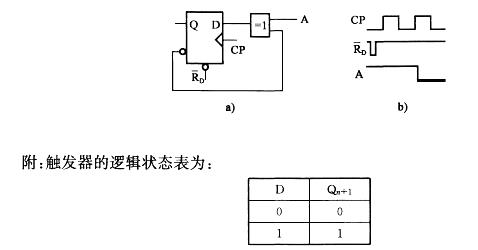

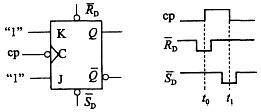

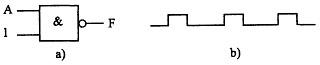

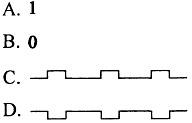

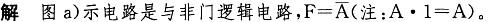

,信号A及时钟脉冲信号cp如图b)所示,经分析可知,在第一个和第二个时钟脉冲的下降沿时刻,输出Q分别等于:

,信号A及时钟脉冲信号cp如图b)所示,经分析可知,在第一个和第二个时钟脉冲的下降沿时刻,输出Q分别等于:

第1题:

A.模拟信号

B.电平信号

C.脉冲信号

D.时钟脉冲信号

第2题:

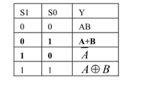

试分析图题4-17所示电路在S、So 信号控制下,其输入A、B与输出Y之间的关系。

第3题:

A、上升沿

B、下降沿

C、高电平

D、低电平

第4题:

第5题:

第6题:

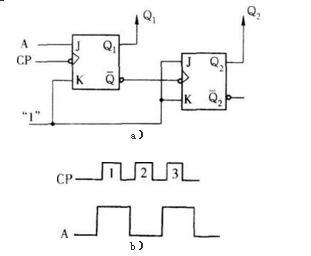

试分别画出图4-30(a)电路输出端Y、Z和图4-30(b)电路输出端Q2的波形.输入信号A和CP的电压波形如图4-30(c)所示,各触发器的初始状态为0.

第7题:

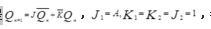

是触发器的异步清零端,由触发器的逻辑功能分析即可得答案。

是触发器的异步清零端,由触发器的逻辑功能分析即可得答案。第8题:

此题为判断题(对,错)。

第9题:

第10题: