地址总线A0(高位)~A15(低位),用4K×4的存储芯片组成16KB存储器,则加至各存储芯片上的地址线是()。

第1题:

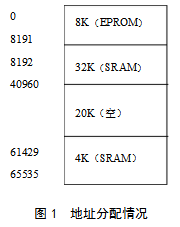

CPU的地址总线16根(A15~A0,A0是低位),双向数据总线16根(D15~D0),控制总线中与主存有关的信号 有!MREQ(允许访存,低电平有效),R/!W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32K地址空间为用户程序区,最后(最大地址)4K地址空间为系统程序工作区。如图1所示。上述地址为十进制,按字编址。现有如下芯片。 EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

略

第2题:

某半导体静态存储器芯片的地址线为A12~A0,数据线D3~D0,若组成容量为64KB存储器,需要该种存储芯片的片数为()

第3题:

存储器组成中,若某块存储芯片采用部分译码法,有2条地址线未使用,则该存储芯片中的每个单元有

A.1个地址号

B.2个地址号

C.3个地址号

D.4个地址号

第4题:

6116(2K×8)芯片的片内地址线和数据线分别是()

第5题:

8088CPU访问I/O接口使用A0~A15位地址。

第6题:

现有如下存储芯片:2K×1的ROM、4K×1的RAM、8K×1的ROM。若用它们组成容量为16KB的存储器,前4KB为ROM,后12KB为RAM ,CPU的地址总线16位。各种存储芯片分别用多少片?

第7题:

一个存储芯片需要地址线12根,数据线4根,则该芯片的容量为()

第8题:

第9题:

有一微机系统,采用CPU的低10位地址线A0~A9作为输入输出口的地址线,系统中接口芯片内部有16个端口地址,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为()。

第10题:

80X86CPU使用的地址信号线为()