8086正常的存储器读/写总线周期由()个T状态组成,ALE信号在()状态内有效,其作用是()。

第1题:

基本总线周期划分为T1、T2、T3和T4四个状态的CPU,当它执行一个正常的存储器读总线周期时,系统规定:读命令在丁2开始时产生,T4开始时结束,则访问存储器地址信号的发出应在( )。

A.T4状态

B.T3状态

C.T2状态

D.T1状态

第2题:

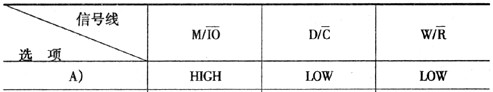

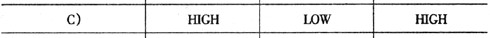

80386有4个总线周期定义信号

但主要的总线周期定义了前三个。在I/O写周期,总线周期定义信号状态为( ),在存储器数据读取周期总线信号定义为( ),在存储器指令码读取周期总线信号定义为( )。

A.

B.

C.

D.

第3题:

A.完成数据传送

B.输出地址

C.输出控制信号

D.检测数据传送

第4题:

“8086执行了一个总线周期”是指8086做了哪些可能的操作?基本总线周期如何组成?在一个典型的读存储器总线周期中,地址信号、ALE信号、/RD信号、数据信号分别在何时产生?

第5题:

8086CPU进行存储器写操作时,在总线周期的T1周期(状态)下,总线信号中()

第6题:

基本总线周期划分为Tl、T2、T3、T4四个状态的CPU,当它执行一个正常的存储器读总线周期时,系统规定:读命令在T2开始时产生,T4开始时结束,则访问存储器地址信号的发生应在( )状态。

A.T4状态

B.T3状态

C.T2状态

D.T1状态

第7题:

第8题:

基本总线周期划分为了T1、T2、T3、T4四个状态的CPU,当它执行一个正常的存储器读总线周期时,系统规定;读命令在T2开始时产生,T4开始时结束,则访问存储器地址信号的发生应在( )状态。

A.T4状态

B.T3状态

C.T2状态

D.T1状态

第9题:

8086正常的存储器读/写总线周期由多少个T状态组成?

第10题:

8086无等待的总线周期由()个T状态组成,Pentium无等待的总线周期由()个T状态组成。如果处理器的时钟频率为100MHz,则每个T状态的持续时间为()