第1题:

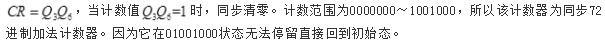

图题 6-24所示为异步4位二进制加法计数器74LS293组成的计数器电路,

试说明该计数电路是多少进制计数器,并说明复位信号RESET的有效电平,

第2题:

第3题:

第4题:

第5题:

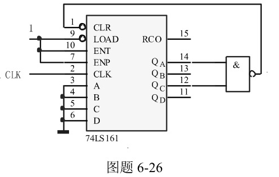

第6题:

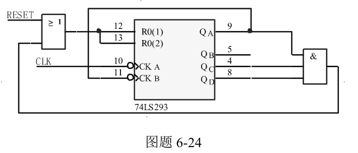

图题6-26所示为具有异步清除功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

第7题:

第8题:

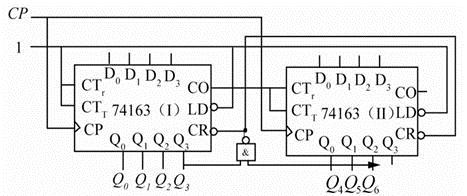

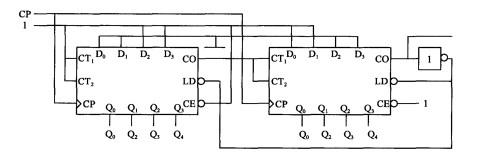

图题6-25所示为具有同步清除功能的同步四位二进制加法计数器74LS163组成的计数器电路,试说明该计数电路是多少进制。

第9题:

第10题: